# Semi Design Presents..

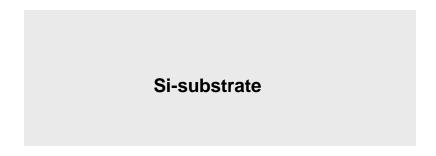

Fig. (1) Pure Si single crystal

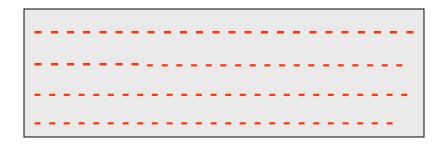

Fig. (2) P-type impurity is lightly doped

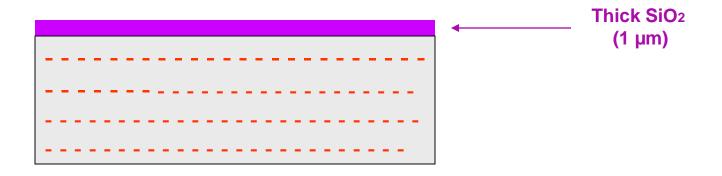

Fig. (3) SiO<sub>2</sub> Deposited over si surface

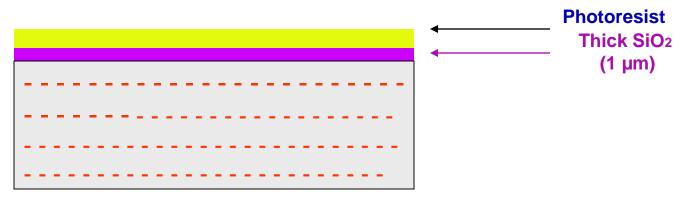

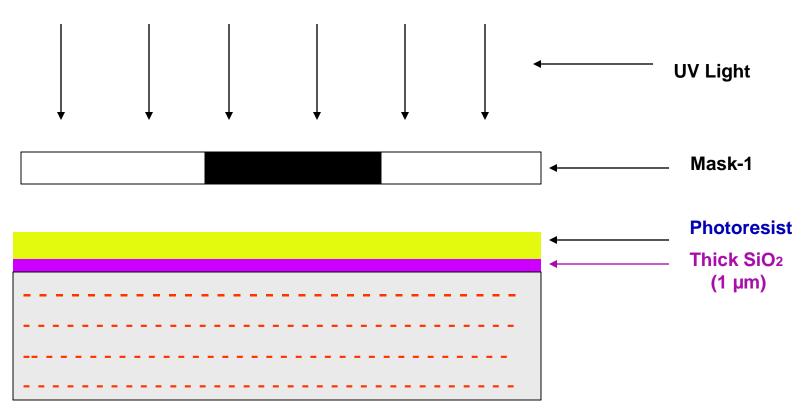

Fig. (4) Photoresist is deposited over SiO<sub>2</sub> layer

Mask-1 is used to expose the SiO<sub>2</sub> where S, D and G is to be formed.

Fig. (5) Photoresist layer is exposed to UV Light through a mask

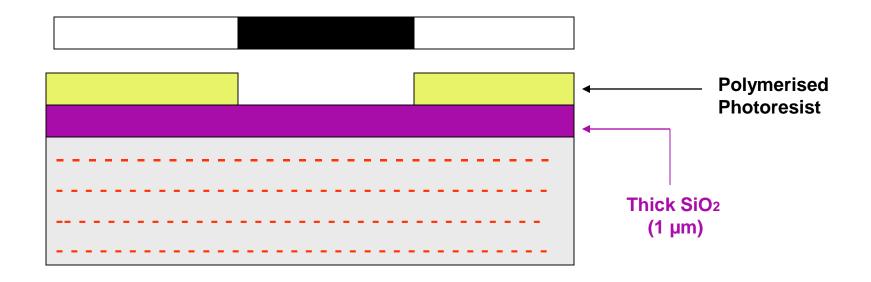

Fig. (6) Developer removes unpolymerised photoresist. It will cause no effect on Si surface

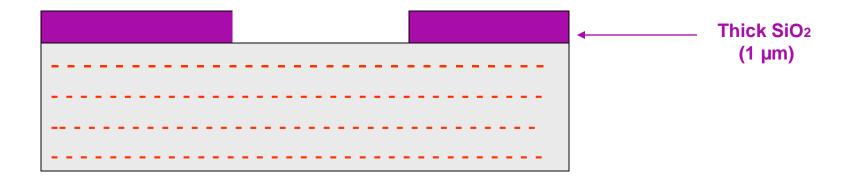

Fig. (7) Etching [HF acid is used] will remove SiO2 layer which is in direct contact with etching solution

Fig. (7) unpolymerised photoresist is also etched away [using H2SO4]

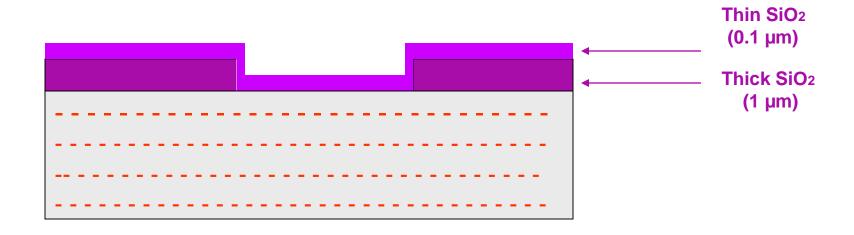

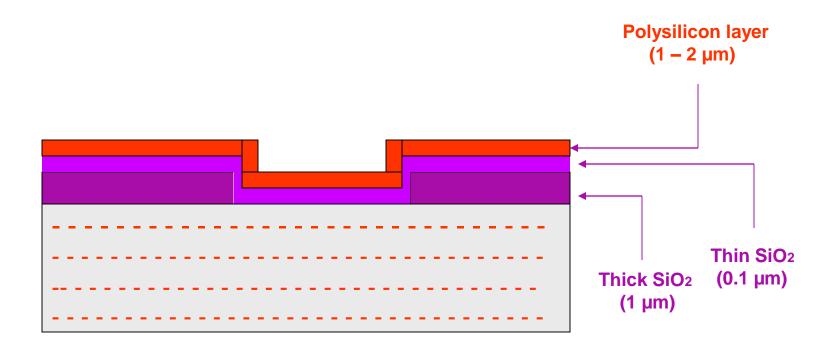

Fig. (8) A thin layer of SiO<sub>2</sub> grown over the entire chip surface

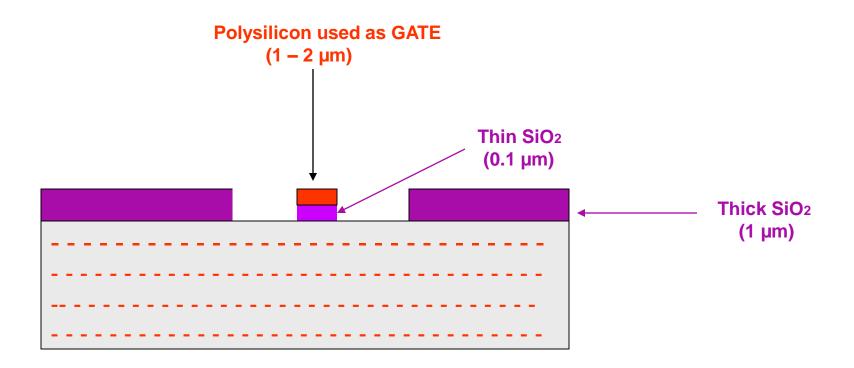

Fig. (9) A thin layer of polysilicon is grown over the entire chip surface to form GATE

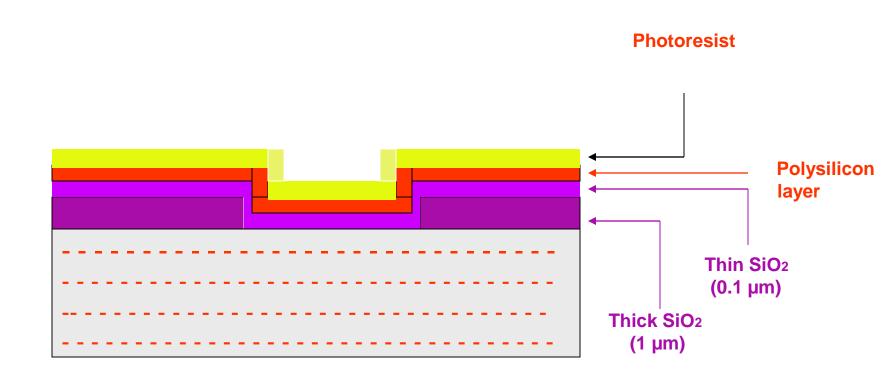

Fig. (10) A layer of photoresist is grown over polysilicon layer

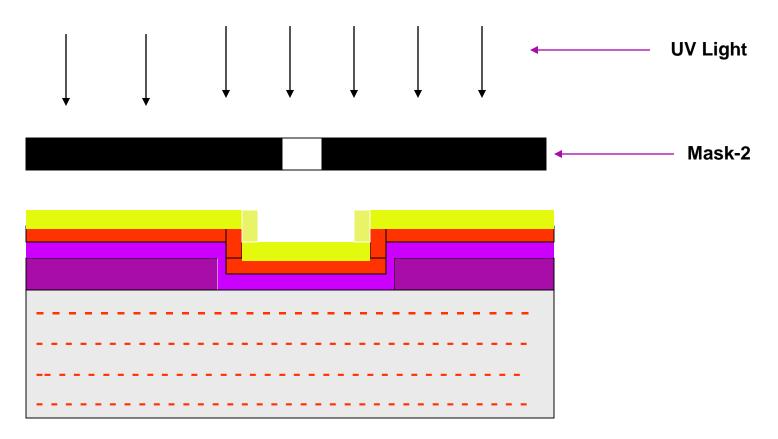

Fig. (11) Photoresist is exposed to UV Light

Mask-2 is used to deposit Polysilicon to form gate.

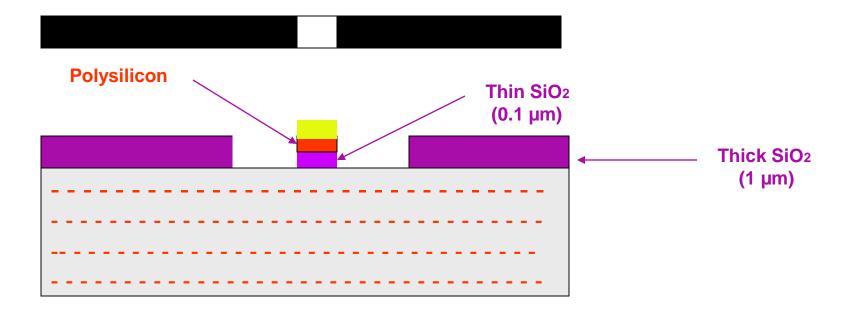

Fig. (12) Etching will remove that portion of Thin SiO2 which is not exposed to UV light

Fig. (13) Polymerised photoresist is also stripped away

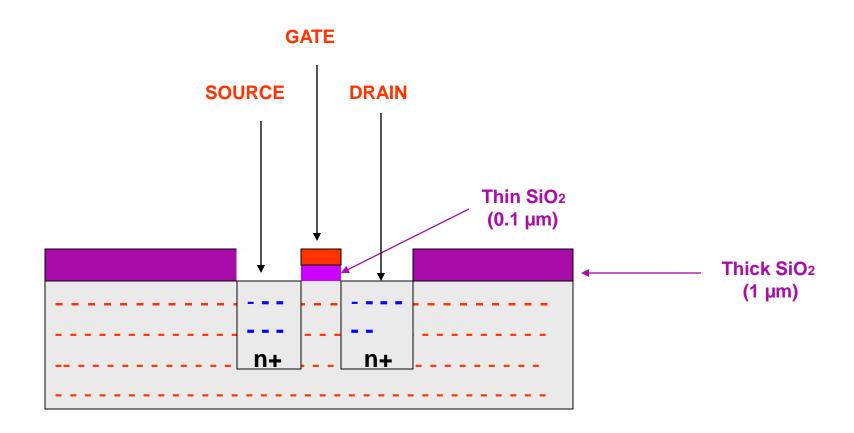

Fig. (14) n<sup>+</sup> Doping to form SOURCE and DRAIN

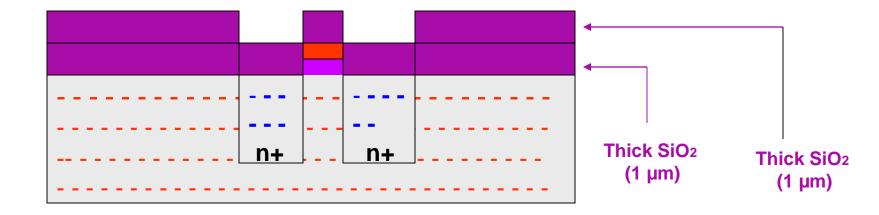

Fig. (15) A thick layer of SiO2 (1  $\mu$ m) is again grown.

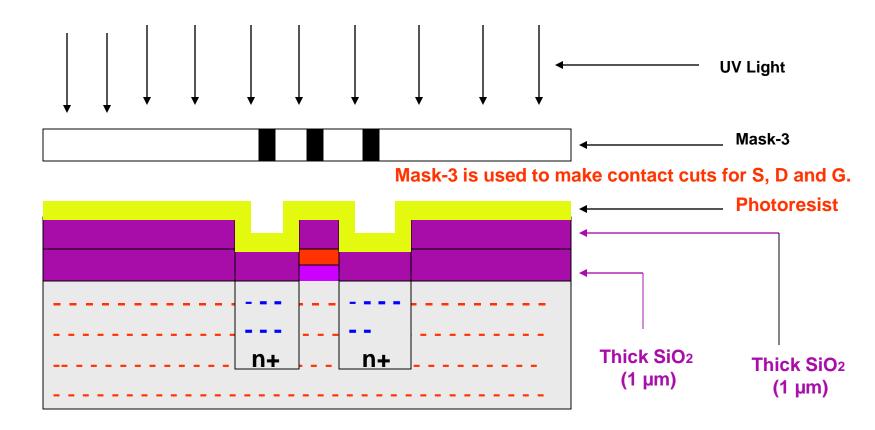

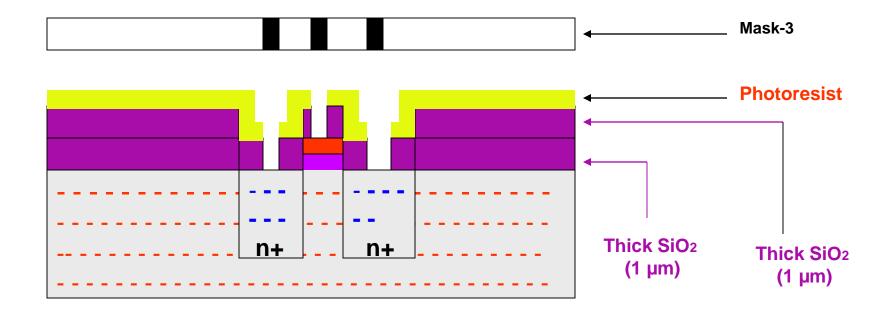

Fig. (16) Photoresist is grown over thick SiO<sub>2</sub>. Selected areas of the poly GATE and SOURCE and DRAIN are exposed where contact cuts are to be made

Fig. (17) The region of photoresist which is not exposed by UV light will become soft. This unpolymerised photoresist and SiO<sub>2</sub> below it are etched away.

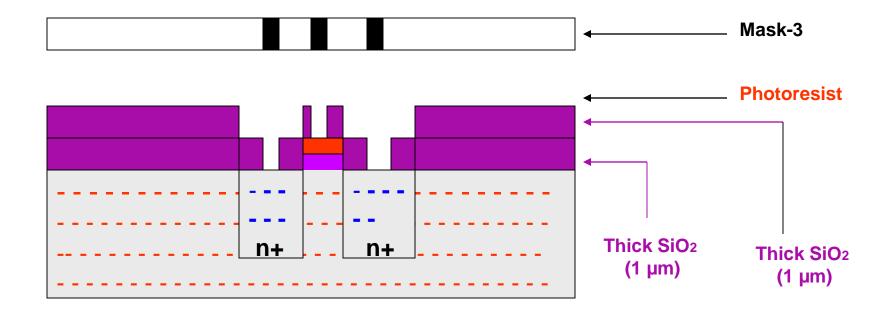

Fig. (18) The contact cuts are formed for S, D and G (hardened photoresist is stripped away).

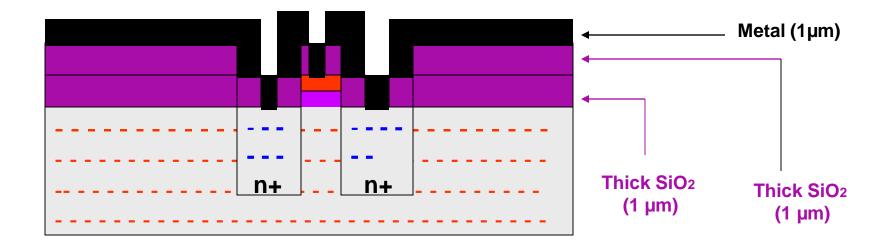

Fig. (19) Metal (aluminium) is deposited over the surface of whole chip (1 µm thickness).

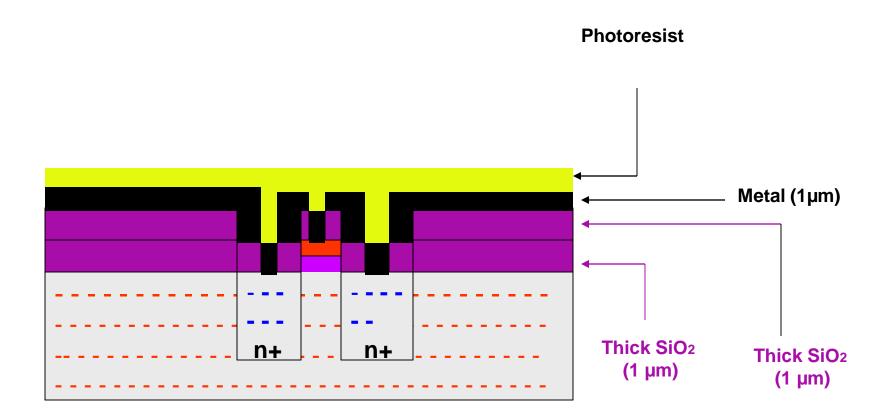

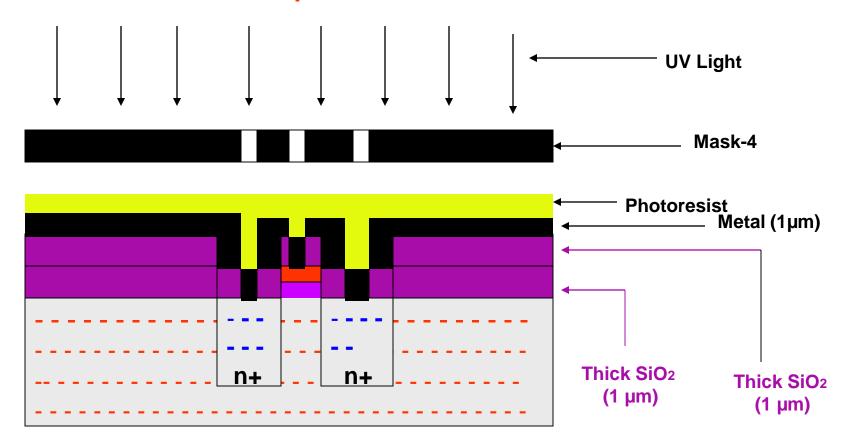

Fig. (20) Photoresist is deposited over the metal.

# **Step - Metallization**

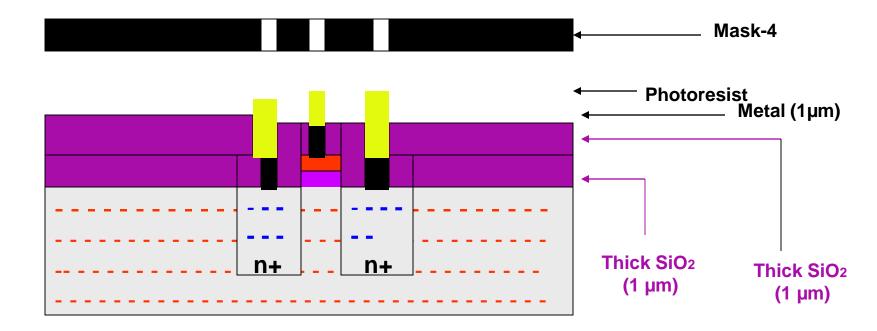

Mask-4 is used to deposit metal in contact cuts of S, D and G.

Fig. (21) UV Light is passed through Mask-4 (with a aim of removing all metal other than metal in contact-cuts).

Fig. (22) Photoresist and metal which is not exposed to UV light are etched away.

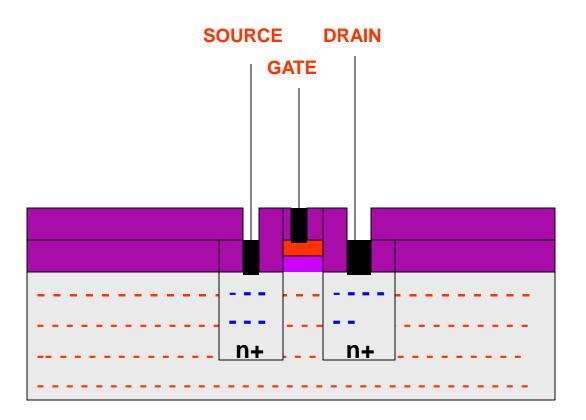

# N-MOS Fabrication Process Step - Metallization

Fig. (23) Final n-MOS Transistor